数字集成电路静态时序分析基础 笔记⑥ 集成电路设计中的时序收敛

引言:从分析到设计

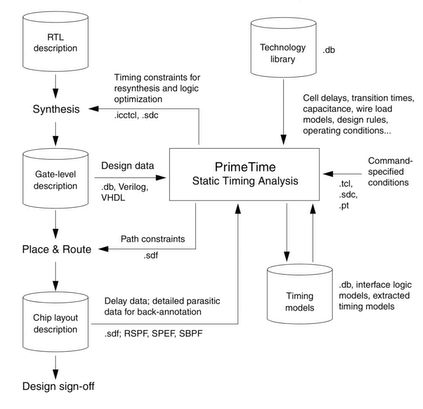

在完成了对建立时间、保持时间、时钟网络、时序路径等基础概念的剖析后,我们的笔记系列最终要回归到 集成电路设计 这一核心目标上。静态时序分析(STA)并非一个孤立的验证环节,而是贯穿于整个设计流程的指导性原则与关键保障。本笔记将探讨如何将STA理论应用于实际设计,以实现 时序收敛 —— 即确保设计在所有工艺角、电压和温度(PVT)条件下都能满足预设的时序要求。

一、 设计流程中的STA介入点

一个典型的数字IC设计流程中,STA是多次迭代进行的:

- 综合阶段(逻辑综合):在将RTL代码映射到目标工艺库的门级网表后,即进行初始的STA。此时主要关注组合逻辑路径的延迟,通过优化逻辑结构、选择驱动能力合适的单元来初步满足时序约束。

- 布局阶段:初步的单元摆放后,可以利用线负载模型进行更精确的时序估算。此时的时序违例主要依靠调整布局、优化高扇出网络来修复。

- 时钟树综合(CTS)后:这是STA的关键节点。时钟网络的实际RC参数确定后,需要进行 带时钟树信息的STA,重点检查时钟偏斜、建立时间和保持时间。此时的保持时间违例会大量出现,需要通过插入缓冲器来修复。

- 布线后:提取实际的寄生参数(RC),进行 签核STA。这是最精确、最严苛的分析,是芯片流片前的最终时序保障。任何在此阶段发现的违例都必须修复。

二、 时序约束的制定:设计的“指挥棒”

STA的准确性极度依赖于 时序约束文件(SDC文件)的完整性。它定义了设计的时序目标,主要包括:

- 时钟定义:创建时钟(周期、占空比、源点)、生成时钟、时钟组、时钟不确定性。

- 输入/输出延迟:定义端口外部世界的时序关系,是分析I/O路径的基础。

- 时序例外:设置虚假路径、多周期路径,避免过度优化,节省面积与功耗。

- 最大/最小延迟约束:对特殊路径进行定制化约束。

关键点:不完整或错误的约束会导致STA结果失真,要么掩盖真正的时序问题(导致流片失败),要么对非关键路径进行过度优化(导致面积功耗浪费)。

三、 实现时序收敛的核心技术与策略

当STA报告显示时序违例(Slack为负)时,设计者需要采取一系列优化手段:

- 针对建立时间违例的优化:

- 逻辑重组:将关键路径上的复杂逻辑分解或重组,减少级联逻辑的深度。

- 尺寸调整:增大关键路径上驱动单元的尺寸(以增加驱动能力,减少本级延迟),或减小其负载单元的尺寸(以减少负载电容)。

- 寄存器重定时:在流水线中移动寄存器的位置,平衡组合逻辑延迟。

- 使用低阈值电压(LVT)单元:在关键路径上使用速度更快但漏电较大的单元,需谨慎权衡功耗。

- 优化时钟网络:减少关键路径的时钟延迟(局部优化),或调整时钟偏斜以帮助特定路径。

- 针对保持时间违例的优化:

- 插入延迟缓冲器:在数据路径上插入缓冲器以增加最小路径的延迟,这是最常用的方法。

- 减小驱动能力:将过快路径上的驱动单元换为尺寸更小的版本,增加其本征延迟。

- 使用高阈值电压(HVT)单元:在非关键路径上使用速度较慢但漏电小的单元,可以自然增加延迟。

- 调整时钟偏斜:在合法范围内,适当增加捕获时钟的延迟(对发射时钟)。

重要原则:建立时间违例的修复通常以增加面积和功耗为代价;而保持时间违例的修复通常以增加面积和微小幅度的功耗为代价。修复过程中需避免“拆东墙补西墙”。

四、 先进工艺下的时序挑战

随着工艺节点进入深亚微米,时序分析变得更加复杂:

- 互连延迟主导:线延迟远超门延迟,使得物理设计与时序分析必须紧密结合(时序驱动布局布线)。

- 工艺变异:片上变异、线边缘粗糙度等要求进行更复杂的 统计静态时序分析,而不能仅依赖角落分析。

- 信号完整性:串扰、电压降会显著影响单元延迟,必须进行带噪声和电源完整性的STA。

- 多模态多角落分析:设计需要在多种工作模式(功能模式、测试模式、省电模式)和数十个甚至上百个PVT条件下同时满足时序,分析量巨大。

五、 STA——设计与制造的桥梁

静态时序分析是现代数字集成电路设计的基石。它从最初RTL代码的综合指导,到最终签核验证,全程为设计“保驾护航”。理解STA,不仅仅是掌握工具命令,更是深入理解 时序模型、电路行为与物理实现 之间的深刻联系。一个优秀的设计工程师,必须能够:

- 编写正确完备的时序约束;

- 解读复杂的STA报告,精准定位瓶颈;

- 运用多种策略,在时序、面积、功耗之间做出最佳折衷;

- 预见先进工艺带来的新挑战,并理解相应的分析流程。

至此,《数字集成电路静态时序分析基础》系列笔记完结。希望这六篇笔记能为你构建一个清晰、坚实的STA知识框架,助你在集成电路设计的道路上走得更稳、更远。

如若转载,请注明出处:http://www.yunkudou.com/product/43.html

更新时间:2026-04-16 22:04:46